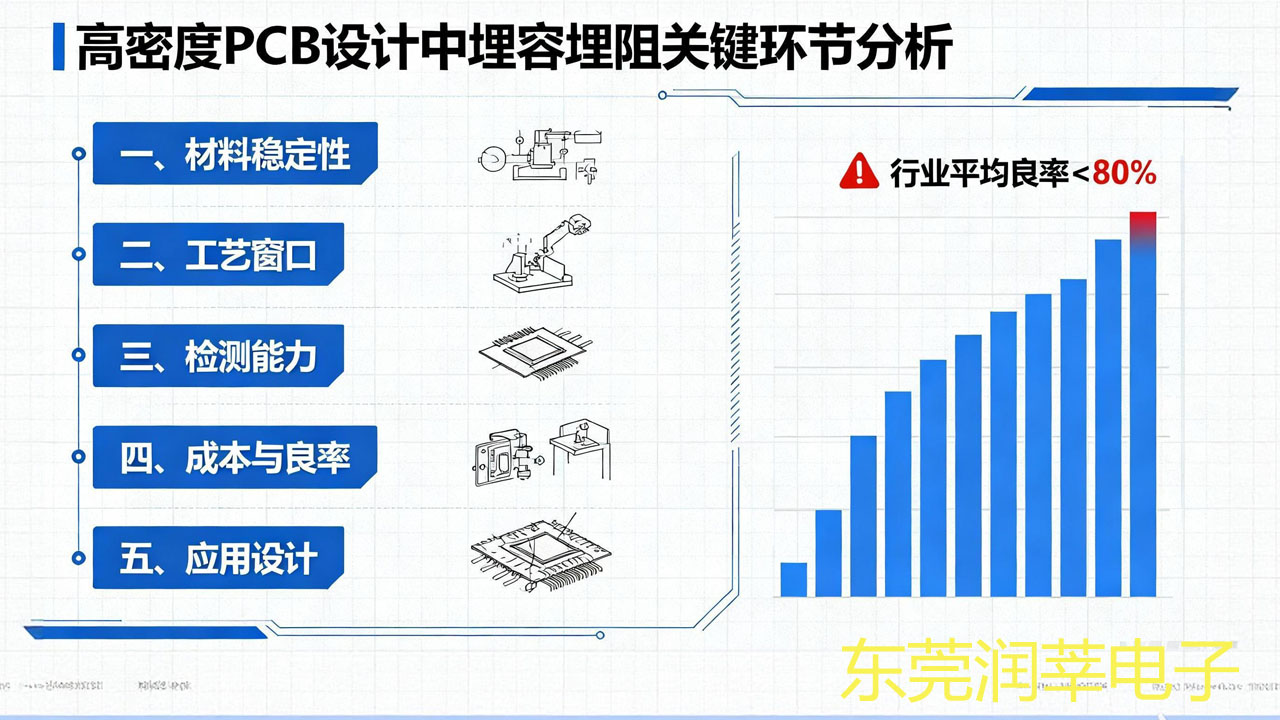

在高密度 PCB 设计中,埋容埋阻因节省空间成为热门选择,但普遍低于 80% 的良率,却让不少企业望而却步。其成熟度之所以未达预期,核心差在 5 个关键环节:

埋容埋阻的核心材料仍缺乏统一标准,稳定性远不及传统 FR4:

• 埋容材料:高介电常数介质薄膜(如 BaTiO₃基),不同批次介电常数偏差可达 ±8%,厚度均匀性误差超 5%(目标≤2%),直接导致电容值波动超 10%;

• 埋阻材料:薄膜电阻(如 NiCr 合金)阻值受温度系数影响大(±100ppm/℃),且材料均匀性差会导致同板阻值偏差超 15%,远高于贴片电阻的 ±1% 标准。

埋容埋阻对工艺精度要求极高,现有工艺控制难以全覆盖:

• 埋容工艺:介质层厚度仅 3-5μm,压合压力偏差>0.2MPa 或温度波动>5℃,就会导致层间气泡;蚀刻线宽偏差>5μm,直接引发短路;

• 埋阻工艺:阻值由蚀刻精度决定,线宽偏差>3μm 即导致阻值偏差超 20%,而多数工厂设备精度仅能控制在 ±5μm,难以满足 ±3μm 的严苛要求。

内嵌特性导致缺陷难以及时发现,成为良率 “隐形杀手”:

• 出厂检测盲区:传统测试设备无法穿透基板检测埋容埋阻的微裂纹(<10μm)、局部短路,约 10%-15% 的缺陷会在 PCBA 装配后暴露;

• 动态检测缺失:电容值、阻值在高温(>85℃)、高湿(RH>85%)环境下的稳定性测试,尚未成为行业标配,部分问题会在使用阶段才显现。

现有技术下,提高良率必然推高成本,难以找到最优解:

• 材料端:选用进口高稳定材料(如日本 JSR 介质薄膜),成本比普通材料高 3-5 倍,良率仅提升 15%-20%;

• 工艺端:增加 3 次全检工序(压合后、蚀刻后、沉铜后),工时增加 50%,成本上升 25%,但良率仍难突破 90%;

• 生产端:为平衡效率,多数工厂选择 “简化检测 + 放宽工艺参数”,直接导致良率维持在 70%-75%。

设计端对工艺边界认知不足,进一步拉低良率:

• 参数超纲:部分设计师要求埋容电容值偏差<5%、埋阻阻值偏差<10%,超出当前工艺稳定范围(实际可稳定控制在 ±15%);

• 集成过度:单块基板内嵌 50 + 埋容埋阻,增加工艺复杂度,良率会随集成数量增加而下降(集成 30 个时良率 80%,集成 50 个时降至 65%)。

本文为东莞润莘电子(www.gdrxs.cn)原创作品,©2025。

未经书面许可,谢绝任何形式的转载、摘编或用于任何商业目的。

欢迎在社交媒体上分享本文链接。