在高端服务器核心板研发中,我们曾寄望埋容埋阻节省空间,却因经验不足连踩 5 个坑,多打 3 轮样板、延误 1 个月周期。以下是最易中招的痛点及实战教训,帮你避开 “交学费” 陷阱:

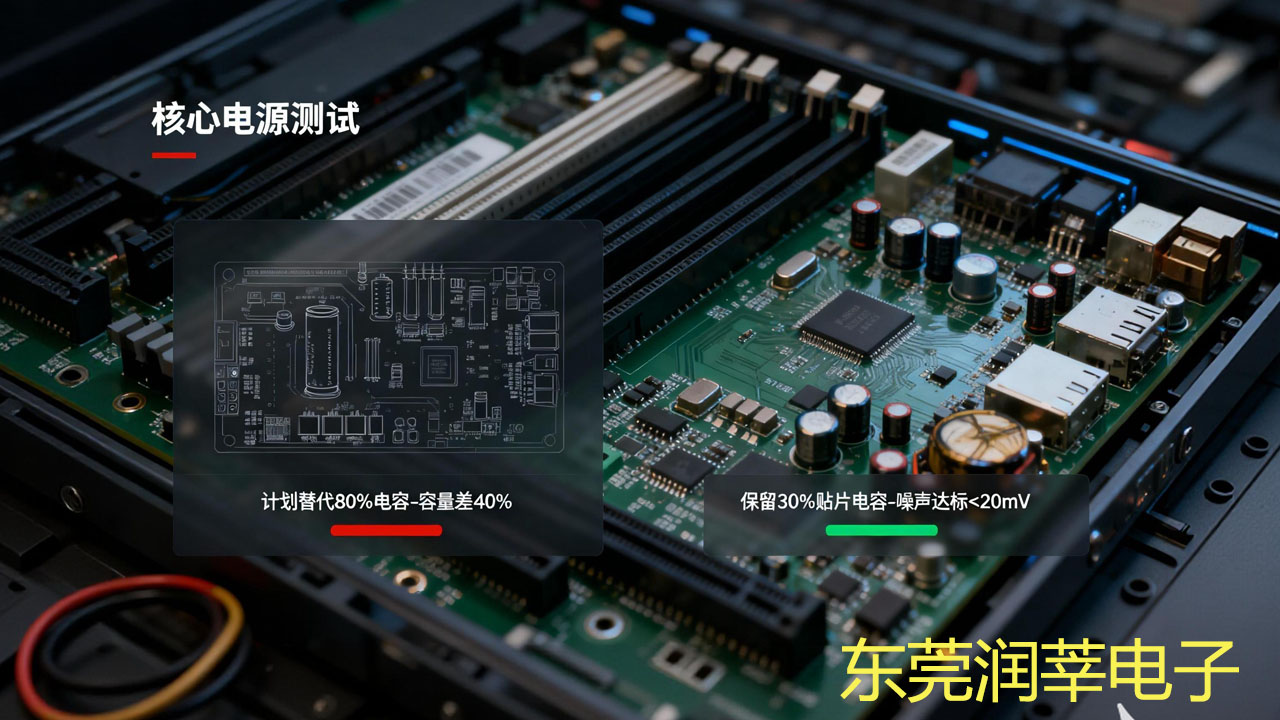

踩坑场景:初期想靠埋容替代 80% 去耦电容,按理论值设计后发现,埋容单位面积电容仅 5nF/cm²(远低于贴片电容的 100nF / 颗),实际叠层能实现的总容量比设计值少 40%,导致电源噪声超标(>50mV),最终被迫额外贴装 20 颗电容,反而浪费空间。

教训:设计前先查板厂埋容实际参数(如介质薄膜类型对应的容量密度),预留 20% 容量冗余;非极端空间需求,保留 30% 贴片电容作为 “备份”,避免全依赖埋容。

踩坑场景:差分终端匹配设计时,选用埋阻替代贴片电阻,忽略其 ±15% 的阻值浮动(贴片电阻仅 ±1%),实际测试眼图抖动超 0.5UI,无法满足服务器高速信号(10Gbps)要求,不得不重新改版布线。

教训:埋阻仅用于上拉 / 下拉、限流等非关键场景;差分匹配、精密分压等对精度要求高的环节,坚决用贴片电阻,避免因阻值偏差影响信号性能。

踩坑场景:按自己设计的叠层(埋容层厚度 3μm、容差 ±5%)画图,送样后板厂反馈 “最小能做 5μm、容差 ±10%”,导致实际电容值偏差超 25%,整批次 50 块样板全部报废,直接损失 2 万元。

教训:设计初期就带着叠层方案找板厂确认 3 个关键参数:埋容最小厚度 / 容量容差、埋阻阻值范围 / 精度,拿到板厂 “工艺可行性报告” 再动笔,避免图纸画完才发现无法落地。

踩坑场景:样机测试发现某路电源噪声超标,想调整埋容容量却无法修改(内嵌后无法更换),只能重新画板、打样,单此延误 20 天;而若用贴片电容,当场更换不同容量即可解决。

教训:核心板关键电源回路,保留 10%-20% 贴片电容点位;设计时在埋容区域预留 “备用焊盘”,方便后期调试时补贴元件,避免全盘依赖埋容导致无法救场。

踩坑场景:未评估实际需求就上埋容埋阻,最终成本比普通方案高 30%(材料 + 工艺溢价),良率却低至 75%(普通板良率 95%),而节省的空间仅 5%,收益远抵不上风险。

教训:只有当服务器核心板空间紧张到 “必须压缩 20% 以上”,或有极端可靠性要求时,才考虑埋容埋阻;常规设计优先选成熟的贴片方案,平衡成本与良率。

本文为东莞润莘电子(www.gdrxs.cn)原创作品,©2025。

未经书面许可,谢绝任何形式的转载、摘编或用于任何商业目的。

欢迎在社交媒体上分享本文链接。